SRI VASAVI ENGINEERING COLLEGE (AUTONOMOUS)

(Sponsored by Sri Vasavi Educational Society) (Approved by AICTE, New Delhi & Recognized by UGC under section 2(f) & 12(B)) (Permanently affiliated to JNTUK, Kakinada, Accredited by NBA and NAAC with 'A' Grade) Pedatadepalli, TADEPALLIGUDEM – 534 101.W.G.Dist. (A.P)

**Department of Electronics and Communication Engineering**

Date: 04.09.2021

#### Minutes of the 5<sup>th</sup> meeting of BOS (Held on 03.09.2021)

The ECE Department 5<sup>th</sup> meeting of Board of Studies (BOS) was conducted through online mode on 03.9.2021 at 11.00 A.M using ZOOM Application with following given link address.

https://us02web.zoom.us/j/83132873142.

Following external members have attended the meeting along with internal faculty members. The ECE HOD, Dr E. Kusuma Kumari, BOS Chairman headed the meeting.

Details of members attended:

| S.No | Name of the BOS<br>Member     | Nominee               | Address                                                             |  |  |

|------|-------------------------------|-----------------------|---------------------------------------------------------------------|--|--|

| 1.   | Dr.E. KusumaKumari            | Chair person          | Professor & Head, ECE, SVEC                                         |  |  |

| 2.   | Prof.I. SanthiPrabha          | University<br>Nominee | Prof. in ECE Dept., University<br>College of Engg., JNTUK, Kakinada |  |  |

| 3.   | Prof. NVSN. Sarma             | Subject Expert        | Director, IIIT Trichy<br>Tiruchirapalli, Tamilnadu.                 |  |  |

| 4.   | Prof. M. VenugopalaRao        | Subject Expert        | Prof., ECE Dept., K.L.University,<br>Vijayawada.                    |  |  |

| 5.   | Sri. Sunkavalli Siva<br>Kumar | Alumni Nominee        | Sr.Engineer,Qualcomm, Bangalore.                                    |  |  |

| 6.   | All Faculty Members in Dept.  | Members               | ECE Dept., SVEC                                                     |  |  |

The following are the key points discussed in the meeting.

- Item No.1 : Chairperson, BOS has welcomed all the members and given the Opening Remarks.

- > Item No.2: Review & Approval of the VII& VIII Sem of B. Tech ECE of V18 Reg.

BOS members Reviewed the Course Structure and given Following Suggestions

- Change the Course title of Radar Systems to Radar Engineering (V18ECT20) in VII semester

- Change the Professional Elective course title from IoT: Concepts & Applications to IoT: Use cases (V18ECT24) in VII semester.

- Removal of topic of "Efficiency of Non Matched Filter in the syllabus of Radar Engg. Course (V18ECT20) in VII Semester.

- Rearrange the syllabus for course titled Optical Communication (V18ECT21) in VII semester.

- Add One more Text book for the Bio-Medical Instrumentation Course (V18ECT35) in VIII semester.

The approved course structure & Syllabus for the VII & VIII semesters of B. Tech ECE of V18 regulation was given in **Annexure-01**

> Item No.3: Review & Approval the List of Open Elective Courses offered by ECE Dept., in VII & VIII Semesters B. Tech ECE of V18 Reg.

BOS Members suggested that to Change the Open elective course title in VII Semester "Principles of Wireless, Cellular Mobile Comm. is to "Principles of Wireless Communication" (V18ECTOE4) and approved the Syllabus.

Approved List of Courses and Syllabus was given in Annexure -02

- Item No. 4: Review & Approval of the Proposed Course Structure and Syllabi for the III and IV Semester of B. Tech ECE under V20 Regulation.

- BOS members reviewed and suggested that try to include Machine Learning Topics in Course titled as Skill Oriented Course (V20ECSOC01) in the III and IV Semester of B. Tech ECE under V20 Regulation and approved the Syllabus.

- In the III semester, the Course titled Probability Theory & Stochastic Processes can be approved in the Basic Science BOS meeting. ECE BOS members were accepted to that proposal.

- Approved the Proposed Course Structure and Syllabi for the III and IV Semester of B. Tech ECE under V20 Regulation.

Approved List of Courses and Syllabus was given in Annexure-03

Item No. 5: Approval of List of Courses offered to EEE Department in III Semester of

B. Tech EEE under V20 Regulation.

BOS members approved the Syllabus and details are given in Annexure-04

- Item No. 6: Approval of Proposed course structure & syllabi for the courses offered in III & IV semesters of B. Tech ECT under V20 Regulation.

BOS members approved the Syllabus and details are given in Annexure -05.

- Item No. 7: Approval of Proposed course structure and Syllabi for M. Tech Programme with specialization of Embedded Systems & VLSI under V21 Regulations. BOS Members Suggested that to include the MOOCS courses in III semester of the M. Tech Programme, approved the Course Structure and Syllabus. The details are given in

#### Annexure -06.

Finally, the chairperson thanked all the BOS members and faculty. The meeting was ended at 12.30 P.M

Dr. E. Kusuma Kumari, Chairperson, BOS

#### <u>Vision</u>

• To develop the department into a centre of excellence and produce high quality, technically competent and responsible Electronics and communication engineers

#### <u>Mission</u>

- To create a learner centric environment that promotes the intellectual growth of the students..

- To develop linkages with R & D organizations and educational institutions for excellence in teaching, learning and consultancy practices.

- To build the student community with high ethical standards.

Approved Course Structure & Syllabus for VII& VIII Semesters

## **COURSE STRUCTURE**

#### (For V18 Regulation)

#### **VII Semester**

| S1.<br>No | Course Code                         | Category                        | Course Title                                                                                                                                  | Hours per<br>week |   | er | Credi<br>ts |  |

|-----------|-------------------------------------|---------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------|-------------------|---|----|-------------|--|

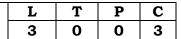

| •         |                                     |                                 |                                                                                                                                               | L                 | Т | Ρ  | С           |  |

| 1         | V18ECT20                            | Professional Core<br>Courses    | Radar Engineering                                                                                                                             | 3                 | 0 | 0  | 3           |  |

| 2         | V18ECT21                            | Professional Core<br>Courses    | Optical Communication                                                                                                                         | 3                 | 0 | 0  | 3           |  |

| 3         | V18ECT22                            | Professional Core<br>Courses    | Digital Image Processing                                                                                                                      | 3                 | 0 | 0  | 3           |  |

| 4         | V18ECT24<br>V18ECT25<br>V18ECT26    | Prof. Elective Course           | <ul> <li>Prof. Elective 3:</li> <li>IOT: Use Cases</li> <li>CMOS Analog IC Design</li> <li>Digital TV Engg.</li> </ul>                        | 3                 | 0 | 0  | 3           |  |

| 5         | V18ECT27<br>V18ECT28<br>V18ECT29    | Prof. Elective Course           | <ul> <li>Prof. Elective 4:</li> <li>Low Power IC Design</li> <li>System On Chip</li> <li>System Design Through<br/>Verilog</li> </ul>         | 3                 | 0 | 0  | 3           |  |

| 6         | V18ECTOE4<br>V18ECTOE5<br>V18ECTOE6 | Open Elective<br>Course         | <ul> <li>Open Elective-2:</li> <li>Principles of Wireless Comm.</li> <li>Medical Electronics</li> <li>Concepts of Embedded Systems</li> </ul> | 3                 | 0 | 0  | 3           |  |

| 7         | V18ECL11                            | Professional Core<br>Course Lab | Microwave & Optical Comm. Lab                                                                                                                 | 0                 | 0 | 2  | 1           |  |

| 8         | V18ECPR01                           | Project                         | Project                                                                                                                                       | 0                 | 0 | 6  | 3           |  |

|           |                                     |                                 | Total                                                                                                                                         | 18                | 0 | 8  | 22          |  |

#### **VIII Semester**

| S1.<br>No | Course Code                         | Category                        | Course Title                                                                                                                                                                                  | Hours per<br>week |   | Cre<br>dit<br>s |    |

|-----------|-------------------------------------|---------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------|---|-----------------|----|

| •         |                                     |                                 |                                                                                                                                                                                               | L                 | Т | Ρ               | С  |

| 1         | V18ECT30                            | Professional Core Course        | Cellular Mobile Communication                                                                                                                                                                 | 3                 | 0 | 0               | 3  |

| 2         | V18ECT31<br>V18ECT32<br>V18ECT33    | Professional Elective<br>Course | <ul> <li>Prof. Elective 5:</li> <li>Electronics Measurements &amp;<br/>Instrumentation</li> <li>FPGA Architecture</li> <li>Principles of Modern Wireless<br/>Communication Systems</li> </ul> | 3                 | 0 | 0               | 3  |

| 3         | V18ECT34<br>V18ECT35<br>V18ECT36    | Professional Elective<br>Course | <ul> <li>Prof. Elective 6:</li> <li>Satellite Communication</li> <li>Biomedical Instrumentation.</li> <li>Wireless Sensor Networks</li> </ul>                                                 | 3                 | 0 | 0               | 3  |

| 4         | V18ECTOE7<br>V18ECTOE8<br>V18ECTOE9 | Open Elective Course            | <ul> <li>Open Elective-3:</li> <li>Fundamentals of Digital Image &amp; Video Processing</li> <li>Embedded RTOS</li> <li>Principles of Digital TV Engg.</li> </ul>                             | 3                 | 0 | 0               | 3  |

| 5         | V18ECPR02                           | Project                         | Project Contd.                                                                                                                                                                                | 0                 | 0 | 16              | 8  |

|           |                                     |                                 | TOTAL                                                                                                                                                                                         | 12                | 0 | 16              | 20 |

## VII-Semester Syllabus

### Course Outcomes: After Successful completion of the Course, the student will be able to:

- CO1: Derive the radar range equation and to solve some analytical problems. [K2]

- CO2: Describe the operation of CW and FMCW Radar systems. [K2]

- CO3: Illustrate the principle of each and every block of MTI and Pulse Doppler Radar [K2]

- CO4: Distinguish the different methods used for tracking targets. [K2]

- CO5: Relate the Noise Figure and Noise Temperature in Radar Receivers [K2]

- CO6: Explain the various components of radar receiver and its performance. [K2]

#### UNIT-I:

**Basics of Radar:** Introduction, Maximum Unambiguous Range, simple Radar range Equation, Radar Block Diagram and Operation, Radar Frequencies and Applications.

**Radar Equation :** Prediction of Range Performance, Minimum Detectable Signal, Receiver Noise, Modified Radar Range Equation, SNR, Probability of Detection, Probability of False Alarm, Integration of Radar Pulses, Radar Cross Section of Targets (simple targets-sphere, cone-sphere), Transmitter Power, PRF and Range Ambiguities, System Losses.

#### UNIT-II:

**CW and Frequency Modulated Radar:** Doppler Effect, CW Radar – Block Diagram, Isolation between Transmitter and Receiver, Non-zero IF Receiver, Receiver Bandwidth Requirements, Applications of CW radar.

**FM-CW Radar:** Range and Doppler Measurement, Block Diagram and Characteristics, FM-CW altimeter, Multiple Frequency CW Radar.

#### UNIT-III:

**MTI and Pulse Doppler Radar:** Introduction, Principle, MTI Radar with - Power Amplifier Transmitter and Power Oscillator Transmitter, Delay Line Cancellers – Filter Characteristics, Blind Speeds, Double Cancellation, Nth Cancellation Staggered PRFs. Range Gated Doppler Filters. MTI Radar Parameters, Limitations to MTI Performance, MTI versus Pulse Doppler Radar. **UNIT –IV:**

**Tracking Radar:** Tracking with Radar, Sequential Lobing, Conical Scan, Mono pulse Tracking Radar – Amplitude Comparison Mono pulse (one- and two- coordinates), Phase Comparison Mono pulse, Tracking in Range, Acquisition and Scanning Patterns, Comparison of Trackers.

#### UNIT –V:

**Detection of Radar Signals in Noise:** Introduction, Matched Filter Receiver – Response Characteristics and Derivation, Correlation Detection and Cross-correlation Receiver, Matched Filter with Non-white Noise, Noise Figure and Noise Temperature.

#### UNIT –VI:

**Radar Receivers** –Displays – types. Duplexers – Branch type and Balanced type, Circulators as Duplexers.

**Introduction to Phased Array Antennas** – Basic Concepts, Radiation Pattern, Beam Steering and Beam Width changes, Series versus parallel feeds, Applications, Advantages and Limitations. **TEXT BOOKS:**

- 1. Introduction to Radar Systems Merrill I. Skolnik, TMH Special Indian Edition, 2<sup>nd</sup>Ed., 2007.

- 2. Radar Principles Peebles, Jr., P.Z., Wiley, New York, 1998.

- 3. Microwave & Radar Engineering G. SasibhushanaRao, Pearson Publications

#### **REFERENCE BOOKS:**

- 1. Introduction to Radar Systems, 3rd edition M.I. Skolnik, TMH Ed., 2005

- 2. Microwave & Radar Engineering M. Kulkarni, Umesh Publications, 3rd edition

- 3. Radar Engineering GSN Raju, IK International.

Р

0

С

3

#### **Syllabus Details**

### Course Outcomes: After Successful completion of the Course, the student will be able to:

CO1: Describe the overview of optical fiber communication, ray theory transmission and Concepts of modes.**[K2]**

CO2: Explain thoroughly the operation of optical sources, Quantum efficiency and power. **[K2]** CO3: Classify different types of optical detectors and also explain the operation of optical Receiver.**[K2**

CO4: Illustrate the concept of power launching and power coupling for optical fibers. Discuss splicing techniques and connector losses. **[K3]**

CO5: Explain the types of fiber materials with their properties and fiber losses. **[K2]** CO6:Construct optical link and becomes familiar with WDM concepts and measurement Techniques.**[K3]**

#### UNIT I

Introduction - Historical development, the general system, advantages of optical fiber communications. Optical fiber wave guides - Ray theory transmission, Total Internal Reflection, Acceptance angle, Numerical Aperture, Skew rays, Cylindrical fibers- Modes, V-number, Mode coupling, Step Index fibers, Graded Index fibers, Single mode fibers - Cut off wavelength, Mode Field Diameter, Effective Refractive Index, Related problems.

#### UNIT II

Optical sources-LEDs, Structures, Materials, Quantum efficiency, Power, Modulation, Power bandwidth product. Injection Laser Diodes- Modes, Threshold conditions, Laser diode rate equations, External quantum efficiency, resonant frequencies, Reliability Considerations.

#### UNIT III

Optical detectors- Physical principles of PIN and APD, Detector response time, Temperature effect on Avalanche gain, Comparison of Photo detectors, Optical receiver operation - Fundamental receiver operation, Digital signal transmission, error sources, Receiver configuration, Digital receiver performance, Probability of Error, Quantum limit, Analog receivers. Related problems.

#### UNIT IV

Fiber materials - Glass, Halide, Active glass, Chalgenide glass, Plastic optical fibers. Signal Degradation in optical fibers - Attenuation, Absorption, Scattering and Bending losses, Core and Cladding losses, Information capacity determination, Group delay, Types of Dispersion: Material dispersion, Wave-guide dispersion, Polarization-Mode dispersion, Intermodal dispersion, Pulse broadening in Graded index fiber, Related problems.

#### UNIT V

Source to fiber power launching-Output patterns, Power coupling, Power launching, Equilibrium Numerical Aperture, Lensing Schemes for Coupling, Laser diode to fiber coupling. Fiber to Fiber joints – Mechanical misalignment, Fiber related losses, End face preparation, Fiber Splicing-Splicing techniques, Splicing single mode fibers, Optical fiber ConnectorsConnector types, Single mode fiber connectors, Connector return loss, Multimode fiber joints, Single mode fiber joints.

#### UNIT VI

Optical system design - Point-to- point links- System considerations, Link power budget, Rise time budget with examples, Line coding in Optical links, Operational Principles of WDM, Measurement of Attenuation and Dispersion, Eye pattern.

#### **TEXT BOOKS:**

1. Optical Fiber Communications – Gerd Keiser, McGraw-Hill International edition, 3rd Edition, 2000.

2. Fiber Optic Communication Systems – Govind P. Agarwal, John Wiley, 3rd Edition, 2004.

#### **RERFERENCES:**

1. Fiber Optic Communications – D.K. Mynbaev, S.C. Gupta and Lowell L. Scheiner, Pearson Education,2005.

2. Text Book on Optical Fiber Communication and its Applications – S.C.Gupta, PHI, 2005.

3. Fiber Optic Communications – Joseph C. Palais, 4th Edition, Pearson Education, 2004.

### Course Outcomes: After Successful completion of the Course, the student will be able to:

CO1. Illustrate the different Transforms Techniques & their use in Image Processing Applications**(K3)**

CO2. Examine Spatial & frequency domain filtering like smoothing & sharpening Operation son Images **(K4)**

CO3. Analyze Restoration operations/techniques on Images(K4)

CO4. Describe the Image compression Techniques and multi-resolution processing on Images**(K3)**

CO5. Analyze morphological operations on Images & Image segmentation(K4)

CO6. Illustrate the different color Image Processing Techniques on Images(K3)

#### UNIT-I

**Introduction:** Introduction to Image Processing, Fundamental steps in digital image processing, components of an image processing system, image sensing and acquisition, image sampling and quantization, some basic relationships between pixels, an introduction to the mathematical tools used in digital image processing.

**Image Transforms:** Need for image transforms, Discrete Fourier transform (DFT) of one variable, Extension to functions of two variables, some properties of the 2-D Discrete Fourier transform, Walsh Transform. Hadamard transform, Haar Transform, Slant transform, Discrete Cosine transform, Discrete Sine Transform, Comparison of different image transforms.

#### UNIT-II

**Intensity Transformations and Spatial Filtering:** Some basic intensity transformation functions, histogram processing, fundamentals of spatial filtering, smoothing spatial filters, and sharpening spatial filters.

**Filtering in the Frequency Domain:** The Basics of filtering in the frequency domain, image Smoothing using frequency domain filters, Image Sharpening using frequency domain filters, Selective filtering.

#### UNIT-III

**Image Restoration and Reconstruction:** A model of the image degradation / Restoration process, Noise models, restoration in the presence of noise only-Spatial Filtering, Periodic Noise Reduction by frequency domain filtering, Linear, Position –Invariant Degradations, Estimating the degradation function, Inverse filtering, Minimum mean square error (Wiener) filtering, geometric mean filter .

#### UNIT-IV

**Image compression:** Fundamentals, Basic compression methods: Huffman coding, Arithmeticcoding,LZWcoding,Run-Lengthcoding,Symbol-Basedcoding,Bit-

Planecoding, BlockTransformcoding,

**Wavelets and Multi resolution Processing:** Image pyramids, sub band coding, Multi resolution expansions, wavelet transforms in one dimensions &two dimensions, Wavelet coding.

#### UNIT-V

**Image segmentation:** Fundamentals, point, line, edge detection, thresholding and region – based segmentation.

**Morphological Image Processing:** Erosion and dilation, opening and closing, basic morphological algorithms for boundary extraction, thinning, gray scale morphology.

#### UNIT-VI

**Color image processing:** color fundamentals, color models, pseudo color image processing, basics of full color image processing, color transformations, smoothing and sharpening. Image segmentation based on color, noise in color images, color image compression.

#### **TextBooks:**

- 1. R.C. Gonzalez and R.E.Woods, Digital ImageProcessing, 3<sup>rd</sup>edition, PrenticeHall, 2008.

- 2. Jayaraman, S. Esakkirajan, and T. Veerakumar, "Digital Image Processing", Tata McGraw-Hill Education, 2011.

#### **Reference Books:**

- 1. AnilK.Jain, "FundamentalsofDigitalImageProcessing", PrenticeHallofIndia, 9th Edition, India nReprint, 2002.

- 2. B.Chanda, D.Dutta Majumder, "Digital ImageProcessingandAnalysis", PHI, 2009.

IOT: Use Cases

С

3

### Course Outcomes: After Successful completion of the Course, the student will be able to:

- CO1: Describe M2M and IOT Technologies. **[K2]**

- CO2: Explain the layers and protocols in IOT. [K2]

- CO3: Describe various communication technologies used in IOT. [K2]

- CO4: Illustrate various hardware components required for IOT applications. [K2]

- CO5: Discuss the cloud technologies and their services. [K2]

- CO6: Explain the IoT Applications. **[K2]**

#### **UNIT I – INTRODUCTION [1]**

Introduction from M2M to IoT - An Architectural Overview, building architecture, Main design principles and needed capabilities, An IoT architecture outline, M2M and IoT Technology Fundamentals - Devices and gateways.

#### UNIT II – IOT PROTOCOLS [2]

Functionality of Layers in IoT –Study of protocols - Wireless HART, Z-Wave, 6LoWPAN, RPL, CoAP, MQTT.

#### **UNIT III - COMMUNICATION TECHNOLOGIES IN IOT [2, 4]**

Study of IoT Connectivity –IEEE 802.15.4, Zigbee, LPWAN, Wi-Fi, Bluetooth, 5G Era.

#### UNIT IV - SYSTEM HARDWARE [3, 4]

Sensors, Actuators, Radio Frequency Identification, Introduction to Embedded Devices for IoT - RASPBERRY PI, BeagleBone black.

#### UNIT V - Cloud Computing [3, 4]

Data Collection, Storage and Computing Using a Cloud Platform for IoT Applications/Services, AWS for IoT-Introduction to Amazon EC2.

#### UNIT VI - IOT APPLICATIONS [2, 3]

Applications - Smart and Connected Cities, Public Safety, Agriculture, and Healthcare.

#### TEXTBOOKS:

- "From Machine-to-Machine to the Internet of Things: Introduction to a New Age of Intelligence", Jan Holler, Vlasios Tsiatsis, Catherine Mulligan, Stefan Avesand, StamatisKarnouskos, David Boyle, 1<sup>st</sup> Edition, Academic Press, 2014.

- 2. IoT Fundamentals: Networking Technologies, Protocols, and Use Cases for the Internet of Things, David Hanes, Gonzalo Salgueiro, Patrick Grossetete, Robert Barton, Jerome Henry, and Cisco Press 800 East 96th Street Indianapolis, Indiana 46240 USA.

- "Internet of Things (A Hands-on- Approach)", Vijay Madisetti and ArshdeepBahga, 1stEdition, VPT, 2014.

- 4. Internet of Things By Raj Kamal, McGraw-Hill Education. Copyright.

#### **REFERENCE BOOKS:**

- 1. From Internet of Things to Smart Cities: Enabling Technologies edited by Hongjian Sun, Chao Wang, Bashar I. Ahmad, CRC Press -2018.

- 2. Bernd Scholz-Reiter, Florian Michahelles, "Architecting the Internet of Things", ISBN 978-3-642-19156-5 e-ISBN 978-3-642-19157-2, Springer.

- 3. IOT (Internet of Things) Programming: A Simple and Fast Way of Learning IOT, David Etter.

### Course Outcomes: After Successful completion of the Course, the student will be able to:

- CO1: Describe the Large and Small signal models of different Analog Devices( K2)

- CO2: Analyse the various types of current mirrors.(K3)

- CO3: Analyse the different types of single stage MOS amplifiers.(K3)

- CO4: Describe the Noise modelling of Various Circuit Elements.(K2)

- CO5: Illustrate the construction and working of OP-AMP.(K3)

- CO6: Illustrate the types of CMOS Comparators .(K3)

#### UNIT -I: Integrated circuit Devices and Modelling

Semiconductors and p-n junction: diodes reverse biased diodes, graded junctions, large signal

junction capacitance and forward biased junctions small signal model of forward biased diode

The MOS Transistor: symbol for MOS Transistors, basic Operation, and Large signal modelling

small signal modelling.

Bi-Polar Transistors: basic Operation, Large signal modelling small signal modelling

#### **UNIT -II: Basic Current Mirrors**

Basic CMOS current Mirrors, source Degenerated current mirror, Cascade current Mirror and

Wilson Current Mirror, bipolar current mirror and Current mirror with Beta Helper.

#### **UNIT -III: Single Stage Amplifiers**

Common source amplifier, Source follower, common gate Amplifier, Cascode Gain stage amplifier

and MOS Differential Amplifiers. Frequency response of Amplifiers.

#### **UNIT -IV: Noise Analysis and Modelling**

Time Domain Analysis of Noise: RMS, SNR, Units of dBm& Noise summation.

Frequency Domain Analysis of Noise: Noise spectral Density, White Noise, Flicker Noise, Noise

filtering & Noise bandwidth.

Noise models for circuit elements: Resistors, Diodes, Transistors and MOSFETS

#### UNIT -V: CMOS Operational Amplifiers & Compensation

Block diagram of Op-amp, op-amp gain, frequency response &Slew Rate, op-amp Compensation

#### **UNIT -IV: Comparators**

Characterization of Comparator, Two-Stage,Open-Loop Comparators, Other Open-Loop Comparators, Improving the Performance of Open-Loop Comparators, Discrete- Time Comparators.

#### **TEXT BOOKS:**

1. Analog Integrated Circuit Design- David A.Johns, Ken Martin, Wiley Student Edn, 2013.

2. CMOS Analog Circuit Design - Philip E. Allen and Douglas R. Holberg, Oxford University Press, International Second Edition/Indian Edition,2010.

#### **REFERENCES:**

1. Analysis and Design of Analog Integrated Circuits- Paul R. Gray, Paul J. Hurst,

S. Lewis and R. G. Meyer, Wiley India, Fifth Edition, 2010.

2. Design of Analog CMOS Integrated Circuits- Behzad Razavi, TMH

Edition, Second Edition

### Course Outcomes: After Successful completion of the Course, the student will be able to:

| ٠ | CO1: Illustrate the fundamentals of television engineering.         | [K2] |

|---|---------------------------------------------------------------------|------|

| ٠ | CO2:Explain the colour TV transmission and reception                | [K2] |

| ٠ | CO3: Compare Digital TV transmission standards                      | [K4] |

| • | CO4: Discuss factors affecting system noise and transmission errors | [K2] |

| ٠ | CO5: Explain the Digital TV transmission and reception.             | [K2] |

| ٠ | CO6: Describe the operation of LCD and Plasma screens               | [K2] |

#### UNIT I

Introduction: TV transmitter and receivers, synchronization

Television Pictures: Geometric form and aspect ratio, image continuity, interlaced scanning, picture resolution

Composite video signal: Horizontal and vertical sync details

TV Signal Transmission: VSB transmission, standard channel BW, TV transmitter

#### UNIT II

**Colour Television:** Perception of brightness and colours, additive colour mixing, video signals for colours, luminance signal, colour difference signals, encoding of colour difference signals, formation of chrominance signals, PAL encoder, PAL colour receiver

#### UNIT III

**Digital Television Transmission Standards:** ATSC terrestrial transmission standard, vestigial sideband modulation, DVB -T transmission standard, ISDB-T transmission standard, channel allocations, antenna height and power, MPEG-2.

#### UNIT IV

**Performance Objectives for Digital Television:** System noise, external noise sources, transmission errors, error vector magnitude, eye pattern, interference, co-channel interference, adjacent channel interference, analog to digital TV, transmitter requirements.

#### UNIT V

**Digital Television**: Digital System Hardware, Signal Quantization and Encoding, Digital Satellite Television, Direct to Home Satellite Television, Digital TV Receiver, Merits of Digital TV Receivers

#### UNIT VI

**LCD and Plasma Screens**: LCD Technology, LCD Matrix types and operation, LCD Screens for Television, Plasma and conduction of charge, Plasma TV Screens, Plasma Color Receiver, LCD color receiver

#### **Text Books:**

1. Modern Television Practice: Transmission, Reception and Applications- R. R.Gulati, 4th Revised edition, New Age International Publishers.

2. Television and Video Engineering – A.M. Dhake, 2nd Edition, Tata McGraw Hill Publishers.

3. Fundamentals of Digital Television Transmission- Gerald W. Collins, John Wiley & Sons.

4. Television engineering and video systems – R G Gupta, Tata McGraw Hill Publishers.

#### References

- 1. Basic Television and Video Systems Bernard Grob, McGrawHill Publishers.

- 2. Monochrome and Colour Television R RGulati, New Age International Publishers.

- 3. Colour Television, Theory and Practice S.P.Bali, Tata McGraw-Hill Publishers.

С

3

#### **Syllabus Details**

### Course Outcomes: After Successful completion of the Course, the student will be able

to:

- CO1: Explain the need of Low power circuit design (K2).

- CO2: Describe the different architectural approaches (K2).

- CO3: Analyze Low-Power Design Approaches(K4).

- CO4: Analyze and design Low-Voltage Low-Power Adders circuits(K4).

- CO5: Analyze and design Low-Voltage Low-Power Multiplier circuits(K4).

- CO6: Analyze and design of Low-Voltage Low-Power Memories(K4).

#### UNIT-I:

**Fundamentals:** Need for Low Power Circuit Design, Sources of Power Dissipation–Switching Power Dissipation, Short Circuit Power Dissipation, Leakage Power Dissipation, Glitching Power Dissipation, Short Channel Effects.

#### UNIT-II:

**Supply Voltage Scaling for Low Power:** Device Feature Size Scaling, Constant-Field Scaling, Constant-Voltage Scaling, Architectural-Level Approaches: Parallelism for Low Power, Pipelining for Low Power, Combining Parallelism with Pipelining.

**Voltage Scaling Using High-Level Transformations:** Multilevel Voltage Scaling Challenges in MVS Voltage Scaling Inter faces, Static Timing Analysis Dynamic Voltage and Frequency Scaling.

#### UNIT-III

#### ${\small Low-PowerDesignApproaches:} Low-PowerDesignthroughVoltageScaling-$

VTCMOScircuits,MTCMOScircuits,ArchitecturalLevelApproach–PipeliningandParallelProcessing Approaches. Power Gating, Clock Gating Versus Power Gating, Power-Gating Issues.

#### UNIT-IV:

**Low-Voltage Low-Power Adders:** Introduction, Standard Adder Cells, CMOS Adder's Architectures – Ripple Carry Adders, Carry Look- Ahead Adders, Carry Select Adders, Carry Save Adders, Low-Voltage Low-Power Design Techniques –Trends of Technology and Power Supply Voltage.

#### UNIT-V

**Low-Voltage Low-Power Multipliers:** Introduction, Overview of Multiplication, Types of MultiplierArchitectures, BraunMultiplier, Baugh-WooleyMultiplier, IntroductiontoWallace Tree Multiplier.

#### UNIT-VI:

**Low-Voltage Low-Power Memories:** Basics of ROM, Low-Power ROM Technology, Future Trend and Development of ROMs, Basics of SRAM, Memory Cell, Pre-charge and Equalization Circuit, Low-Power SRAM Technologies, Basics of DRAM, Self-Refresh Circuit, Future Trend and Development of DRAM.

#### **TEXTBOOKS:**

1. CMOS Digital Integrated Circuits–Analysis and Design–Sung-Mo Kang, Yusuf Leblebici, TMH,2011.

2. Low-Voltage, Low-Power VLSI Subsystems-Kiat-SengYeo,KaushikRoy,TMH ProfessionalEngineering,1st edition,2004

#### **REFERENCEBOOKS:**

1. IntroductiontoVLSISystems:ALogic,CircuitandSystemPerspective–Ming-BO Lin, CRCPress,2011

2. Low Power CMOS VLSI Circuit Design – Kaushik Roy, Sharat C. Prasad, JohnWiley& Sons, 2000.

3. Practical Low Power Digital VLSI Design–Gary K.Yeap, Kluwer AcademicPress, 2002.

4. Leakage in Nanometer CMOS Technologies-SivaG.Narendran,Anatha

Chandrakasan, Springer, 2005.

С

3

#### **Syllabus Details**

### Course Outcomes: After Successful completion of the Course, the student will be able to:

- CO1: Describe SOC System Approach, design and its Architecture.[K2]

- CO2: Discuss the selection of processor and its micro architecture for SOC[K2]

- CO3: Describe Memory Design for SOC [K2]

- CO4: Explain the concepts of bus models and Interconnect Architectures **[K2]**

- CO5: Describe the overview of Zynq SOC[K2]

- CO6: Explain the SOC based Applications. **[K2]**

**UNIT – I: Introduction to the System Approach:** System Architecture, Components of the system, Hardware & Software, Processor Architectures, Memory and Addressing. System level interconnection, an approach for SOC Design, System Architecture and Complexity.

**UNIT – II : Processors**: Introduction , Processor Selection for SOC, Basic concepts in Processor Architecture, Basic concepts in Processor Micro Architecture, Basic elements in Instruction handling. Buffers: minimizing Pipeline Delays, Branches, More Robust Processors, Vector Processors and Vector Instructions extensions, VLIW Processors, Superscalar Processors.

**UNIT – III : Memory Design for SOC**: Overview of SOC external memory, Internal Memory, Size, Scratchpads and Cache memory, Cache Organization, Cache data, Write Policies, Strategies for line replacement at miss time, Types of Cache, Split – I, and D – Caches, Multilevel Caches, Virtual to real translation , SOC Memory System, Models of Simple Processor – memory interaction.

**UNIT – IV : Interconnect Customization and Configuration:** Inter Connect Architectures, Bus: Basic Architectures, SOC Standard Buses, Analytic Bus Models, Using the Bus model, Effects of Bus transactions and contention time. SOC Customization: An overview, Customizing Instruction Processor, Reconfiguration Technologies, Mapping design onto Reconfigurable devices, Instance Specific design, Customizable Soft Processor.

UNIT-V: Zynq system on chip design overview: interfacing and signals, interconnects, Memory and interrupts.

**UNIT – VI: Application Studies / Case Studies**: SOC Design approach, Design and evaluation - AES algorithms, Image compression – JPEG compression.

#### **TEXT BOOKS:**

- 1. Computer System Design System-on-Chip Michael J. Flynn and Wayne Luk, Wiely India Pvt. Ltd.

- Embedded Processing with the ARM Cortex-A9 on the Xilinx Zynq-7000 All Programmable SoC-Louise H. Crockett Ross A. Elliot Martin A. Enderwitz Robert W. Stewart

- Design of System on a Chip: Devices and Components Ricardo Reis, 1st Ed., 2004, Springer

#### **REFERENCE BOOKS:**

1. Co-Verification of Hardware and Software for ARM System on Chip Design

(Embedded Technology) - Jason Andrews - Newnes, BK and CDROM.

2. System on Chip Verification - Methodologies and Techniques - Prakash Rashinkar,

Peter Paterson and Leena Singh L, 2001, Kluwer Academic Publishers.

| VII<br>Sem. | System Design Through      | VERILOG Course Code:V18ECT29 | L | Т | Р | C |

|-------------|----------------------------|------------------------------|---|---|---|---|

|             | VERILOG                    |                              | 3 | 0 | 0 | 3 |

|             | (Professional Elective-IV) |                              | 3 | U | 0 | 3 |

### Course Outcomes: After Successful completion of the Course, the student will be able to:

| • | CO1: Outline basic concepts of RTL code for digital circuits           | K2 |

|---|------------------------------------------------------------------------|----|

| ٠ | CO2: Model RTL codes for digital circuit at gate level                 | K3 |

| ٠ | CO3: Model RTL codes for digital circuit at behavioural level          | К3 |

| ٠ | CO4: Model RTL codes for digital circuit at data flow and switch level | К3 |

| • | CO5: Ouline the concepts of task, function and complier directives     | K2 |

|   | COG. Analyze Symthesize of Combinational and Seguential Cinquite       | VA |

CO6: Analyze Synthesize of Combinational and Sequential Circuits

K4

#### UNIT-I INTRODUCTIONTOVERILOG:

Verilog as HDL, Levels of design description, concurrency, module, simulation and synthesis, test bench, functional verification, programming language interface (PLI), simulation and synthesis tools.

#### LANGUAGECONSTRUCTSANDCONVENTIONS:

Introduction, keywords, identifiers, whitespace characters, comments, numbers, strings, logic values, data types, scalars and vectors, parameters, memory, operators, system tasks.

#### UNIT-II GATELEVELMODELLING:

Introduction, and gate primitive, module structure, other gate primitives, illustrative examples, tristate gates, array of instances of primitives, design of Flip flops with gate primitives, delays, strengths and contention resolution, net types, design of basic circuits.

#### UNIT-III BEHAVIORALMODELLING:

Introduction, operations and assignments, initial construct, always construct, examples, assignments with delays, wait construct, multiple always blocks, designs at behavioral level, blocking and nonblocking assignments, the case statement, if and if else constructs, assign-De assign construct, repeat construct, FOR loop, the disable construct, While loop, Forever loop, parallel blocks, forcerelease construct, event.

#### UNIT-IV DATA FLOWLEVEL MODELLING

Introduction, continuous assignment structures, delays and continuous assignments, assignment to vectors.

#### SWITCH LEVEL MODELLING

Basic transistor switches, CMOS switch, Bidirectional gates and time delays with switch primitives, instantiations with strengths and delays, strength contention with triregnets, switch level modeling for NAND, NOR and XOR.

#### UNIT-V

**SYSTEM TASKS, FUNCTIONS, AND COMPILER DIRECTIVES:** Introduction, System Tasks and Functions, File based Tasks and Functions, Compiler Directives, Hierarchical Directives, User-defined Primitives (UDP), FSM Design (Moore and Melay Machines).

#### UNIT-VI

**SYNTHESISOFCOMBINATIONAL ANDSEQUENTIAL LOGIC USINGVERILOG:** Synthesis of Combinational logic: Net list of structured primitives, a set of continuous assignment statements and level sensitive cyclic behavior with examples, Synthesis of priority structures, exploiting logic don't care conditions.

Synthesis of sequential logic with latches: Accidental synthesis of latches and Intentional synthesis of latches, Synthesis of sequentiallogic with flip-flops, Synthesis of explicit statemachines.

#### **TEXTBOOKS:**

- 1. Design through VerilogHDL —T.R.PadmanabhanandB. BalaTripuraSundari, WSE,IEEEPress,2004.

- 2. Advanced Digital Design withVerilog HDL—MichaelD.Ciletti,PHI,2005.

#### **REFERENCES:**

- 1. FundamentalsofLogicDesignwithVerilog—Stephen.BrownandZvonkoVranesic,TMH,2005.

- 2. AVerilogPrimier—J.Bhasker,BSP,2003.

С

1

#### Syllabus Details

### Course Outcomes: After Successful completion of the Course, the student will be able to:

- CO1. Sketch the characteristics of various Microwave & Optical sources **(K3)**

- CO2. Compute the various Parameters of Microwave & Optical Components (K3)

- CO3. Measure the radiation pattern of Horn antenna and reflector antenna. **(K5)**

- CO4. Analyze a rectangular microstrip patch antenna using HFSS software **(K4)**

#### Minimum Twelve Experiments to be conducted:

#### Part – A (Any 7 Experiments):

- 1. Reflex Klystron Characteristics.

- 2. Gunn-Diode Characteristics.

- 3. Attenuation Measurement.

- 4. Directional Coupler Characteristics.

- 5. Impedance and Frequency Measurement.

- 6. Scattering parameters of Circulator.

- 7. Scattering parameters of Magic Tee.

- 8. Radiation Pattern of Horn and Parabolic Antennas.

- 9. Synthesis of Microstrip antennas (Rectangular Structure) Using HFSS.

#### Part – B (Any 5 Experiments):

- 10. Characterization of LED.

- 11. Characterization of Laser Diode.

- 12. Intensity modulation of Laser output through an optical fiber.

- 13. Measurement of Data rate for Digital Optical link.

- 14. Measurement of NA.

- 15. Measurement of losses for Analog Optical link.

#### **Equipment required for Laboratories:**

- 1. Klystron Power Supply, Klystron mount

- 2. VSWR Meter

- 3. Micro Ammeter

- 4. Multi meter

- 5. CRO

- 6. GUNN Power Supply, Pin Modulator

- 7. Crystal Diode detector

- 8. Attenuator

- 9. Frequency Meter

- 10. Slotted line carriage

- 11. Probe detector

- 12. Wave guide shorts

- 13. SS Tuner

- 14. Directional Coupler

- 15. E, H, Magic Tees

- 16. Circulators, Isolator

- 17. Matched Loads

- 18. Pyramidal Horn and Parabolic Antennas

- 19. Turntable for Antenna Measurements

- 20. HFSS Software

- 21. Fiber Optic Analog Trainer based LED

- 22. Fiber Optic Analog Trainer based laser

- 23. Fiber Optic Digital Trainer

- 24. Fiber cables (Plastic, Glass)

# VIII-Semester Syllabus

### Course Outcomes: After Successful completion of the Course, the student will be able to:

- CO1: Demonstrate the limitations of conventional mobile telephone systems; Understand the concepts of cellular systems. **[K2]**

- CO2: Illustrate the concept of frequency Reuse channels, deduce Co- channel Interference reduction factor **[K2]**

- CO3: Understand the frequency management, channel assignment strategies and Antennas in cellular systems.**[K2]**

- CO4:Discuss the concepts of Handoff, dropped calls and cell splitting, Intersystem Handoff. **[K2]**

- CO5: Explain the knowledge about GSM architecture and GSM channels, multiple Access schemes like FDMA,TDMA and CDMA. **[K2]**

- CO6: Summarize the concepts of upcoming technologies like 3G, 4G etc. [K2]

**UNIT-I CELLULAR MOBILE RADIO SYSTEMS**: Introduction to Cellular Mobile System, uniqueness of mobile radio environment, operation of cellular systems, consideration of the components of Cellular system, Hexagonal shaped cells, Analog and Digital Cellular systems.

CELLULAR CONCEPTS: Evolution of Cellular systems, Concept of frequency reuse, frequency reuse ratio, Number of channels in a cellular system, Cellular traffic: trunking and blocking, Grade of Service; Cellular structures: macro, micro, pico and femto cells; Cell splitting, Cell sectoring.

**UNIT-II INTERFERENCE**: Types of interferences, Introduction to Co-Channel Interference, real time Co-Channel interference, Co-Channel measurement, Co-channel Interference Reduction Factor, desired C/I from a normal case in a Omni directional Antenna system, design of Antenna system, antenna parameters and their effects, diversity receiver, non-cochannel interference-different types.

**UNIT-III FREQUENCY MANAGEMENT AND CHANNEL ASSIGNMENT:** Numbering and grouping, setup access and paging channels, channel assignments to cell sites and mobile units: fixed channel and non-fixed channel assignment, channel sharing and borrowing, overlaid cells. CELL COVERAGE FOR SIGNAL AND TRAFFIC: Signal reflections in flat and hilly terrain, effect of human made structures, phase difference between direct and reflected paths, straight line path loss slope, and general formula for mobile propagation over water and flat open area, near and long distance propagation, antenna height gain, form of a point to point model.

**UNIT-IV HANDOFF STRATEGIES** Concept of Handoff, types of handoff, handoff initiation, delaying handoff, forced handoff, mobile assigned handoff, intersystem handoff, vehicle locating methods, dropped call rates and their evaluation.

**UNIT-V DIGITAL CELLULAR NETWORKS**: GSM architecture, GSM channels, multiple access schemes; FDMA, TDMA, CDMA, OFDMA;

**UNIT-VI HIGHER GENERATION CELLULAR STANDARDS**: 3G System architecture (UMTS) enhancements in 4G standard, Architecture and representative protocols, introduction to 5G.

#### **TEXTBOOKS:**

1. Mobile Cellular Telecommunications – W.C.Y. Lee, Tata McGraw Hill, 2rd Edn, 2006.

2. Principles of Mobile Communications – Gordon L. Stuber, Springer International 2<sup>nd</sup>Edition, 2007.

#### **REFERENCES:**

1. Wireless Communications – Theodore. S. Rapport, Pearson education, 2nd Edn, 2002.

2. Wireless and Mobile Communications – Lee McGraw Hills, 3rd Edition, 2006. 3. Mobile Cellular Communication – G Sasibhushana Rao Pearson

3. Wireless Communication and Networking – Jon W. Mark and Weihua Zhqung, PHI, 2005.

4. Wireless Communication Technology - R. Blake, Thompson Asia Pvt. Ltd., 2004.

#### <u>Syllabus Details</u>

### Course Outcomes: After Successful completion of the Course, the student will be able to:

CO1. Select the instrument to be used based on the requirements.[K2]

CO2. Understand the design of oscilloscopes for different applications.[K2]

CO3. Explain different signal generators and analyzers.[K2]

CO4. Understand the design of different types of Bridge circuits for different

#### Applications.[K2]

CO5. Explain and Design different types of transducers for different Applications. **[K2]**

CO6. Explain different types of transducers for measurement of Physical parameters. **[K2]**

#### UNIT-I

Performance characteristics of instruments, Static characteristics, Accuracy, Resolution, Precision, Expected value, Error, Sensitivity. Errors in Measurement, Dynamic Characteristics- speed of response, Fidelity, Lag and Dynamic error. DC Voltmeters- Multirange, Range extension/Solid state and differential voltmeters, AC voltmeters- multirange, range extension, shunt. Thermocouple type RF ammeter, Ohmmeters series type, and shunt type, Multi-meter for Voltage, Current and resistance measurements.

#### UNIT-II

Oscilloscopes CRT features, vertical amplifiers, horizontal deflection system, sweep, trigger pulse, delay line, sync selector circuits, simple CRO, triggered sweep CRO, Dual beam CRO, Dual trace oscilloscope, sampling oscilloscope, storage oscilloscope, digital readout oscilloscope, digital storage oscilloscope, Lissajous method of frequency measurement, standard specifications of CRO, Probes for CRO-Active & Passive, attenuator types.

#### UNIT-III

Signal Generator- fixed and variable, AF oscillators, Standard and AF sine and square wave signal generators, Function Generators, Square pulse, Random noise, sweep, Arbitrary waveform. Wave Analyzers, Harmonic Distortion Analyzers, Spectrum Analyzers, Digital Fourier Analyzers.

#### UNIT-IV

DC Bridges: Measurement of Resistance-Wheatstone's Bridge, Kelvin's Bridge. AC Bridges: Measurement of inductance- Maxwell's bridge, Hay's bridge, Anderson Bridge. Measurement of capacitance-Schering's Bridge. Measurement of Frequency-Wien Bridge, Errors and precautions in using bridges.Q-meter.

#### UNIT-V

Transducers- active & passive transducers : Resistance, Capacitance, inductance; Strain gauges, LVDT, Piezo Electric transducers, Resistance Thermometers, Thermocouples, Thermistors, Sensistors.

#### UNIT-VI

Measurement of physical parameters- Force, Pressure, Velocity, Acceleration, Humidity, Moisture, Proximity, Displacement.Data acquisition systems.

#### **TEXTBOOKS:**

- 1. Electronic Instrumentation, second edition-H.S. Kalsi, Tata McGrawHill,2004.

- 2. Modern Electronic Instrumentation and Measurement Techniques-A.D. Helfrick and

W.D.Cooper, PHI, 5thEdition, 2002.

#### **REFERENCES:**

- 1. Electronic Instrumentation & Measurements- David A. Bell, PHI, 2<sup>nd</sup>Edition, 2003.

- 2. Electronic Test Instruments, Analog and Digital Measurements-Robert A. Witte, Pearson Education, 2<sup>nd</sup>Edition, 2004.

3. Electronic Measurements & Instrumentations by K. LalKishore, Pearson Education-2005.

4. Electronic Measurements & Instrumentation by UdayA.Bakshi& Ajay V. Bakshi Technical Publications

#### Course Outcomes: After Successful completion of the Course, the student will be able to:

- CO1: Describe Low end programmable devices.[K2]

- Explain FPGA basics.[K2] CO2:

- Comprehend Spartan 6 basics.[K2] CO3:

- Use Virtex 5 clock sources and FIFO. Comprehend various I/O standards.[K2] CO4:

- CO5: Use Memory, DSP blocks in complex designs. Comprehend SerDes.[K2]

- Comprehend JTAG. Distinguish RISC based Soft processors from Xilinx, Aletra.[K2] CO6:

#### UNIT-I

#### **DESIGNING WITH PROGRAMMABLE LOGIC DEVICES:**

Read only Memories, Programmable logic Arrays (PLA), Programmable Array logic (PAL), Programmable logic Devices (PLD) Skew, setup, hold time.

#### **UNIT-II**

#### **DESIGNING WITH FPGA:**

Logic implementation options, Technology trends, Simple SRAM programmable FPGA architecture, Xilinx 3000 series FPGAs, Programmable interconnects, Xilinx 4000 series FPGAs, Programming the FPGA.

#### **UNIT-III**

#### **SPARTAN 6 ARCHITECUTUTE:**

Spartan 6 Device features- 6 input LUT, Slice, Single Port RAM, Dual Port RAM, ROM, Distributed RAM, 32 x 6, 64 x 1, 128 x 1, Distributed RAM timings, Shift Registers, Multiplexers, Interconnect, PLL, DCM, DSP Slice.

#### **UNIT-IV**

#### **VIRTEX 5 ARCHITECTURE:**

Clock resources-Global clocks, regional clocks, Clock buffer, Clock Gating.Clock Tree, Clock De-skew, True Dual port RAM. Write modes, FIFO architecture, empty flags, almost empty flags, almost fill flags, full flag, cascading FIFOS, connecting FIFOs in parallel, designing Large multiplexer 4xl, 8xl, 16xl. Control impedance, I/O primitives. I/O supported standards, LVDS.

#### **UNIT-V**

#### **STARATIX V ARCHITECTURE:**

ALM Block diagram, ALM operating modes, ALM in Arithmetic mode, Types of embedded memory, Control clocking, Memory features, Memory modes, DSP block features, operational modes, DSP block architecture in 27 X 27 mode, independent complex multiplier mode, I/O features mixing voltage referenced and non-voltage referenced standard I/O features standards. Dynamic OCT.LVDS SerDes block diagram and features, Differential Receiver Block diagram and features.

#### UNIT-VI SOFT PROCESSORS:

JTAG, programming through JTAG, IEEE 1149.1 Boundary scan testing, programmable power technology, Features of Soft processors, Nios-II, Microblaze.

#### **TEXT BOOKS:**

- 1. Charles H Roth Jr "Digital System Design using VHDL", second edition, 2008.

- 2. Spartan 6 family overview.

- 3. Virtex 5- User Guide.

- 4. Staratix V Device Hand Book.

- 5. Nios-II, Microblaze Features Altera, Xilinx.

#### **REFERENCES:**

1. J. Old Field, R.Dorf, "Field Programmable Gate Arrays", John Wiley & Sons, New York, 1995.

- 2. S. Trimberger, Edr. "Field Programmable Gate Arrays Technology", Kluwer Academic Publications, 1994.

- 3. Bob Zeidman, "Designing with FPGAs & CPLDs", CMP Books, 2002.

CO1: Describe how to measure the performance of wireless system, in multipath Environment **[K2]**

CO2: Summarize about Wireless Channel. [K2]

CO3: Explain Principle and properties of CDMA. [K2]

CO4: Discuss the working and advantages of MIMO wireless communication systems [K2]

CO5: Explain the principle and advantages of OFDM system[K2]

CO6: Describe of various modern wireless communication technologies [K2]

#### UNIT-I

**Principles of Wireless Communication**: The wireless communication environment, modelling of wireless systems, system model for narrowband signals, Rayleigh fading wireless channel, BER performance of wireless systems, channel estimation in wireless systems, Diversity in wireless communication, multiple antenna receive model, BER in multiple antenna system, channel estimation in multiple antenna system.

#### UNIT-II

**Wireless Channel:** Basics of Wireless Channel Modelling, Maximum Delay Spread, RMS Delay Spread, RMS Delay Based on Average Power Profile, Average Delay Spread in Outdoor Cellular Channels, Coherence Bandwidth in Wireless Communications, Relation between ISI and Coherence Bandwidth.

#### UNIT-III

**Code Division Multiple Access**: Fundamentals of CDMA codes, Spreading codes based on Pseudo-Noise sequences, correlation properties of random CDMA spread sequences, Multiuser CDMA, Advantages of CDMA, CDMA near far problem and power control.

#### UNIT-IV

**Multiple Input Multiple Output Wireless Communications**: Introduction to MIMO wireless Communications, MIMO System model, MIMO zero forcing (ZF) receiver, MIMO MMSE receiver, Singular Value Decomposition (SVD) of the MIMO channel, MIMO capacity, Asymptotic MIMO capacity, MIMO beam forming.

#### UNIT-V

**Orthogonal Frequency Division Multiplexing**: Introduction to OFDM, multicarrier transmission, cyclic prefix in OFDM, BER for OFDM, MIMO-OFDM, effect of frequency offset in OFDM, Peak to Average Power ratio in OFDM, SC-FDMA.

#### UNIT-VI

**Recent advancements in wireless technology**: Introduction to 4G LTE, VoLTE, 5G Technology, NOMA and Massive MIMO.

#### Text Books:

Aditya K. Jagannatham, "Principle of Modern Wireless Communication Systems: Theory and practice" 1st Edition, McGrawHill Publication

Theodore S. Rappaport, "Wireless Communications: Principles and Practice" Second Edition, Pearson Education

#### **Reference Books:**

Simon Haykin, MichaleMoher, "Modern Wireless Communications", Pearson.

Xiaodong Wang, H. Vincent Poor, "Wireless Communication Systems: Advanced Techniques for Signal Reception", Pearson 5 Proakis J.J.,D Wozencraft J.M. and Jacobs I.M., Principles of Communication Engineering, John Wiley

## Course Outcomes: After Successful completion of the Course, the student will be able to:

CO1. Describe the basic concepts of Satellite Communications & analyze the concepts of Orbital mechanics & Launchers **(K4)**

CO2.Discuss the major Sub-Systems of a Satellite (K2)

CO3.Design the Communication Link for Satellite (K4)

CO4.Compare the various Multiple Access Techniques (K3)

CO5.Analyze the various sub-systems used in Earth stations & review the different orbits

#### (K4)

CO6.Analyze the Satellite Navigation & the Global positioning system (K4)

#### UNIT-I

**Introduction:** Origin of Satellite Communications, Historical Back-ground, Basic Concepts of Satellite Communications, Frequency allocations for Satellite Services, Applications, Future Trends of Satellite Communication.

**Orbital Mechanics and Launchers:** Orbital Mechanics, Look Angle determination, Orbital perturbations, Orbit determination, launches and launch vehicles, Orbital effects in communication systems performance.

#### UNIT-II

**Satellite Subsystems:** Attitude and orbit control system, telemetry, tracking, Command &monitoring, power systems, communication subsystems, Satellite antenna Equipment reliability and Space qualification.

#### UNIT-III

**Satellite Link Design:** Basic transmission theory, system noise temperature and G/T ratio, Design of down links, up link design, Design of satellite links for specified C/N, System design example.

#### UNIT-IV

**Multiple Access:** Frequency division multiple access (FDMA), Inter modulation, Calculation of C/N. Time division Multiple Access (TDMA), Frame structure, Examples. Satellite Switched TDMA Onboard processing, DAMA, Code Division Multiple access (CDMA), Spread spectrum transmission and reception.

#### UNIT-V

**Earth Station Technology:** Introduction, Transmitters, Receivers, Antennas, Tracking systems, Terrestrial interface, Primary power test methods.

**Low Earth Orbit and Geo-Stationary Satellite Systems:** Orbit consideration, coverage and frequency considerations, Delay & Throughput considerations, System considerations, Operational NGSO constellation Designs

#### UNIT-VI

**Satellite Navigation & The Global Positioning System:** Radio and Satellite Navigation, GPS Position Location principles, GPS Receivers and codes, Satellite signal acquisition, GPS Navigation Message, GPS signal levels, GPS receiver operation, GPS C/A code accuracy, Differential GPS.

#### **Text Books:**

1. Satellite Communications – Timothy Pratt, Charles Bostian& Jeremy Allnutt, WSE, Wiley Publications, 2<sup>nd</sup> Edition, 2003.

2. Satellite Communications Engineering – Wilbur L. Pritchard, Robert A Nelson & Henri G. Suyderhoud, 2<sup>nd</sup> Edition, Pearson Publications, 2003.

#### **References:**

1. Satellite Communication: Design Principles – M. Richharia, BS Publications, 2nd Edition, 2003.

- 2. Satellite Communication D.C Agarwal, Khanna Publications, 5th Ed.

- 3. Fundamentals of Satellite Communications K.N. Raja Rao, PHI, 2004

- 4. Satellite Communications Dennis Roddy, McGraw Hill, 2nd Edition, 1996.

## Course Outcomes: After Successful completion of the Course, the student will be able to:

- CO1: Explain the basics concepts of Bio-Medical Instrumentation. **[K2]**

- CO2: Explain the concepts of electrode theory, classification of Electrodes and Transducers used in Bio-Medical Applications.**[K2]**

- CO3: Explainhe Anatomy and Physiology of Cardiovascular system and Illustrate the application of Bio-Medical Instruments to measure the Physiological parameters of Cardiovascular System.**[K2]**

- CO4: Discuss the processing methods in elements used for Patient's Health care & monitoring.**[K2]**

- CO5: Explain the Principles of Diagnostic Techniques and the concepts of Bio-Telemetry.**[K2]**

- CO6: Classify different types of monitors, discuss the principles of recorders and Illustrate the methods of accident preventions i.e. Shock Hazards from different Electrical Equipment.**[K2]**

#### UNIT-I:

**INTRODUCTIONTOBIOMEDICALINSTRUMENTATION:**AgeofBiomedicalEngineering,Develop ment of Biomedical Instrumentation, Man Instrumentation System, Components of the Man-Instrument System, Physiological System of the Body, Problems Encountered in Measuring a Living System, Sources of Bioelectric Potentials, Muscle, Bioelectric Potentials, Sources of Bioelectric Potentials, Resting and ActionPotentials,BioelectricPotentials-ECG,EEGandEMG,EvokedResponses.

#### UNIT-II:

**ELECTRODES AND TRANSDUCERS:** Introduction, Electrode Theory, Bio potential Electrodes, Examples of Electrodes, Basic Transducer Principles, The Transducer and Transduction Principles, Active Transducers, Passive Transducers, Transducers for Biomedical Applications, Pulse Sensors, Respiration Sensor, Transducers with Digital Output.

#### UNIT-III:

**CARDIOVASCULAR SYSTEM AND MEASUREMENTS:** The Heart and Cardiovascular System, Electro Cardiography, Blood Pressure Measurement, Measurement of Blood Flow and Cardiac Output, Measurement of Heart Sounds, Plethysmography.

**MEASUREMENTSINTHERESPIRATORYSYSTEM:** The Physiology of The Respiratory System, Tests and Instrumentation f or the Mechanics of Breathing, Respiratory Therapy Equipment.

#### UNIT-IV:

#### $\label{eq:patient} \textbf{PATIENTCAREANDMONITORING:} Elements of Intensive-$

CareMonitoring,PatientMonitoringDisplays, Diagnosis, Calibration and Repair ability of Patient-Monitoring Equipment, Other Instrumentation for Monitoring Patients, Organization of the Hospital for Patient-Care Monitoring, Pacemakers, Defibrillators.

#### UNIT-V:

**DIAGNOSTIC TECHNIQUES AND BIO-TELEMETRY:** Principles of Ultrasonic Measurement, UltrasonicImaging,UltrasonicApplicationsofTherapeuticUses,UltrasonicDiagnosis,X-RayandRadio-

IsotopeInstrumentations,CATScan,EmissionComputerizedTomography,MRI,IntroductiontoBio telemetry,Physiological Parameters Adaptable to Biotelemetry, The Components of Biotelemetry System, Implantable Units, Telemetry for ECG Measurements during Exercise, Telemetry for Emergency Patient Monitoring

#### UNIT-VI:

**MONITORS, RECORDERSANDSHOCKHAZARDS:** Bio potential Amplifiers, Monitors, Recorders, Shock Hazards and Prevention, Physiological Effects and Electrical Current, Shock Hazards from Electrical Equipment, Methods of Accident Prevention, Isolated Power Distribution System.

#### **Text Books:**

- 1. "Bio-Medical Electronics and Instrumentation", Onkar N.Pandey, Rakesh Kumar, Katson Books.

- 2. "Bio-Medical Instrumentation", Cromewell, Wiebell, Pfeiffer

#### **References:**

- 1. "HandBookofBio-MedicalInstrumentation", Khandapur.McGrawHill

- 2. "IntroductiontoBio-MedicalEquipmentTechnology",4thEdition,JosephJ.Carr,John M.Brown,PearsonPublications.

### Course Outcomes: After Successful completion of the Course, the student will be able to:

- CO1: Explain the concepts of Wireless Sensor Networks, its Architecture. **[K2]**

- CO2: Describe the Networking Technologies. [K2]

- CO3: Explain the MAC Protocols. [K2]

- CO4: Illustrate the Routing Protocols. **[K2]**

- CO5: Describe the Transport Layer Protocols. [K2]

- CO6: Explain the Security Layer Protocols and Applications of WSN. [K2]

#### **UNIT-I –Introduction to Wireless Sensor Networks:**

Key definitions of sensor networks, Advantages of sensor Networks, Unique constraints and challenges, Driving Applications, Enabling Technologies for Wireless Sensor Networks. Single-Node Architecture - Hardware Components, Energy Consumption of Sensor Nodes, Operating Systems and Execution Environments, Network Architecture -Sensor Network Scenarios, Gateway Concepts.

#### **UNIT-II - Networking Technologies**:

Physical Layer and Transceiver Design Considerations, Personal area networks (PANs), hidden node and exposed node problem, Topologies of PANs, MANETsand WANETs.

#### **UNIT-III - MAC Protocols for Wireless Sensor Networks**:

Issues in Designing a MAC protocol for Ad Hoc Wireless Networks, Design goals of a MAC Protocol for Ad Hoc Wireless Networks, Classifications of MAC Protocols - Contention - Based Protocols, with reservation Mechanisms, and with Scheduling Mechanisms.

#### **UNIT-IV - Routing Protocols**:

Introduction, Issues in Designing a Routing Protocol for Ad Hoc Wireless Networks, Classification of Routing Protocols, Table–Driven Routing Protocols, On – Demand Routing Protocols, Hierarchical Routing Protocols, Proactive Routing.

#### **UNIT-V - Transport Layer Protocols**:

Introduction, Issues in Designing a Transport Layer Protocol for Ad Hoc Wireless Networks, Design Goals of a Transport Layer Protocol for Ad Hoc Wireless Networks, Classification of Transport Layer Solutions, TCP Over Ad Hoc Wireless Networks.

#### UNIT- VI - Security, Platforms & Applications:

Security in Ad Hoc Wireless Networks, Network Security Requirements, Issues and Challenges in Security Provisioning; Sensor Node Hardware – Berkeley Motes, Programming Challenges; Applications - Home Automation, Smart Metering.

#### **TEXT BOOKS:**

- 1. Ad Hoc Wireless Networks: Architectures and Protocols, C. Siva Ram Murthy and B.S.Manoj, 2004, PHI.

- 2. Wireless Adhoc and Sensor Networks: Protocols, Performance and Control, JagannathanSarangapani, CRC Press.

- 3. Holger Karl & Andreas Willig, "Protocols and Architectures for Wireless Sensor Networks", John Wiley, 2005.

#### **REFERENCES:**

- 1. Wireless Sensor Networks- Technology, Protocols, and Applications, KazemSohraby, Daniel Minoli, &TaiebZnati, John Wiley, 2007.

- 2. Wireless Sensor Networks- Information Processing Approach, Feng Zhao & Leonidas J. Guibas, Elsevier, 2007.

- 3. Adhoc Mobile Wireless Networks: Protocols & Systems, C.K. Toh,1<sup>st</sup> Ed., Pearson Education.

- 4. Wireless Sensor Networks C. S. Raghavendra, Krishna M. Sivalingam, 2004, Springer.

- 5. Wireless Sensor Networks S Anandamurugan, Lakshmi Publications.

### Approved List of Open Elective- II Courses

### **VII Semester**

| S.No | Course<br>Code | Name of the Course                         | Department Offered                         |

|------|----------------|--------------------------------------------|--------------------------------------------|

| 1    | V18ECTOE4      | Principles of Wireless Comm.               |                                            |

| 2    | V18ECTOE5      | Medical Electronics                        | Electronics & Communication<br>Engineering |

| 3    | V18ECTOE6      | Concepts of Embedded Systems               |                                            |

| 4    | V18CSTOE04     | Operating Systems                          |                                            |

| 5    | V18CSTOE05     | Artificial Intelligence                    | Computer Science<br>Engineering.           |

| 6    | V18CSTOE06     | Java Programming                           | Lingineering.                              |

| 7    | V18EEOE4       | Non-Conventional Energy Sources            |                                            |

| 8    | V18EEOE5       | Electrical Engineering Materials           | Electrical & Electronics<br>Engineering    |

| 9    | V18EEOE6       | Servicing of Electrical Appliances         |                                            |

| 10   | V18MEOE4       | Computer Aided Design                      |                                            |

| 11   | V18MEOE5       | Condition Monitoring & Machine<br>learning | - Mechanical Engineering                   |

| 12   | V18CEOE03      | Environmental Pollution and<br>Control     | - Civil Engineering                        |

| 13   | V18CEOE04      | Disaster Management                        |                                            |

### **Approved List of Open Elective- III Courses**

### **VIII Semester**

| S.No | Course<br>Code | Name of the Course                                  | Department Offered                         |

|------|----------------|-----------------------------------------------------|--------------------------------------------|

| 1    | V18ECTOE7      | Fundamentals of Digital Image &<br>Video Processing |                                            |

| 2    | V18ECTOE8      | Embedded RTOS                                       | Electronics & Communication<br>Engineering |

| 3    | V18ECTOE9      | Principles of Digital TV Engg                       |                                            |

| 4    | V18CSTOE07     | Software Testing Methodologies                      |                                            |

| 5    | V18CSTOE08     | Cyber Security                                      | Computer Science<br>Engineering.           |

| 6    | V18CSTOE09     | Computer Graphics                                   |                                            |

| 7    | V18EEOE7       | Energy Storage Systems                              |                                            |

| 8    | V18EEOE8       | Basics of Electrical Power<br>Generation            | Electrical & Electronics<br>Engineering    |

| 9    | V18EEOE9       | Industrial Automation                               |                                            |

| 10   | V18MEOE6       | Power Plant Engineering                             | Mechanical Engineering                     |

| 11   | V18MEOE7       | Mechatronics                                        |                                            |

| 12   | V18CEOE05      | Solid Waste Management                              |                                            |

| 13   | V18CEOE06      | Water Quality and Conservation                      | Civil Engineering                          |

С

3

#### **Syllabus Details**

### Course Outcomes: After Successful completion of the Course, the student will be able to:

- CO1: Discuss the cellular system evolution of mobile radio systems **[K2**]

- CO2: Illustrate the basic cellular concepts. **[K2]**

- CO3: Explain the Various Propagation models. [K2]

- CO4: Discuss the need of modulation, diversity and equalization in cellular & Mobile Communication. **[K2]**

- CO5: Demonstrate the knowledge about GSM architecture, multiple access schemes like FDMA,TDMA, CDMA. **[K2]**

- CO6: Summarize the concepts of upcoming technologies like 3G, 4G etc. [K2]

#### **UNIT-I: Introduction of Wireless Communication**

History and evolution of mobile radio systems: Types of mobile wireless services/systems-Cellular, WLL, Paging, Satellite systems, Future trends in personal wireless systems.

#### **UNIT-II: Cellular Concepts and System Design Fundamentals**

Cellular concept and frequency reuse, channel assignment, handoff strategies, Interference and system capacity, Trunking and GOS, cell splitting, cell sectoring.

#### **UNIT-III: Mobile radio Propagation Models**

Radio wave propagation issues in personal wireless systems, Propagation models, Multipath fading, parameters of mobile multipath channels and Antenna systems in mobile radio.

#### UNIT-IV: Overview analog and digital modulation techniques

Need For Modulation. Different Analog and Digital modulation techniques used in Cellular and mobile communication systems.

**UNIT-V DIGITAL CELLULAR NETWORKS**: GSM architecture, GSM Services, multiple access schemes; FDMA, TDMA, CDMA, OFDMA;

**UNIT-VI Higher Generation Cellular Standards**: 3G System architecture (UMTS), 4G System Architecture, Introduction to 5G.

#### Text Books

- 1. Theodore S. Rappaport, "wireless communications Principles and Practices", PHI, 2005

- 2. Jochen Schiller, "Mobile Communications", Pearson Education, second edition, 2009.

#### **Reference Book**

- 1. Lee W.C.Y, "Mobile communication Engineering

- 2. Theory and Applications", 2/e McGraw-Hill,New York, 2003

- 3. Andreas F. Molisch, "Wideband Wireless Digital Communication", Pearson Education 2001.

- 4. Blake, "Wireless Communication Technologies," Thomson Delmer, 2003

### Course Outcomes: After Successful completion of the Course, the student will be able to:

- CO1: Explain the basics concepts of Bio-Medical Instrumentation.[K2]

- CO2: Explain the concepts of electrode theory, classification of Electrodes and Transducers used in Bio-Medical Applications.**[K2]**

- CO3: Explainthe Anatomy and Physiology of Cardiovascular system and Illustrate the application of Bio-Medical Instruments to measure the Physiological Parameters of Cardiovascular System. **[K2]**

- CO4: Discuss the elements used for Patient's Health care & monitoring.[K2]

- CO5: Explain the Principles of Diagnostic Techniques and the concepts of Bio-Telemetry.**[K2]**

- CO6: Classify different types of monitors, discuss the principles of recorders and Illustrate the methods of accident preventions.**[K2]**

#### UNIT-I:

**INTRODUCTION TO BIOMEDICAL INSTRUMENTATION:** Age of Biomedical Engineering, Development of Biomedical Instrumentation, Man Instrumentation System, Components of the Man-Instrument System, Physiological System of the Body, Problems Encountered in Measuring a Living System, Sources of Bioelectric Potentials, Muscle, Bioelectric Potentials, Sources of Bioelectric Potentials, Resting and Action Potentials, Bioelectric Potentials-ECG, EEG and EMG,

#### UNIT-II:

**ELECTRODES AND TRANSDUCERS:** Introduction, Electrode Theory, Biopotential Electrodes, Examples of Electrodes, Basic Transducer Principles, Active Transducers, Passive Transducers, Transducers for Biomedical Applications, Pulse Sensors, Respiration Sensor, Transducers with Digital Output.

#### UNIT-III:

**CARDIOVASCULAR SYSTEM AND MEASUREMENTS:** The Heart and Cardiovascular System, ElectroCardiography, Blood Pressure Measurement, Measurement of Blood Flow and Cardiac Output, Measurement of Heart Sounds, Plethysmography.

#### UNIT-IV:

#### $\label{eq:patient} \textbf{PATIENTCAREANDMONITORING:} Elements of Intensive-$

CareMonitoring,PatientMonitoringDisplays, Diagnosis, Calibration and Repair ability of Patient-Monitoring Equipment, Other Instrumentation for Monitoring Patients, Organization of the Hospital for Patient-Care Monitoring, Pacemakers, Defibrillators.

#### UNIT-V:

**DIAGNOSTIC TECHNIQUES AND BIO-TELEMETRY:** Principles of Ultrasonic Measurement, UltrasonicImaging,UltrasonicApplicationsofTherapeuticUses,UltrasonicDiagnosis,X-RayandRadio-

IsotopeInstrumentations,CATScan,EmissionComputerizedTomography,MRI,IntroductiontoBio telemetry,Physiological Parameters Adaptable to Biotelemetry, The Components of Biotelemetry System, Implantable Units, Telemetry for ECG Measurements during Exercise, Telemetry for Emergency Patient Monitoring.

#### UNIT-VI:

**MONITORS, RECORDERS AND SHOCK HAZARDS:** Bio potential Amplifiers, Monitors, Recorders, Shock Hazards and Prevention, Physiological Effects and Electrical Current, Shock Hazards from Electrical Equipment, Methods of Accident Prevention.

#### Text Books:

1. "Bio-MedicalElectronicsand Instrumentation", Onkar N.Pandey, RakeshKumar, Katson Books.

2."Bio-Medical Instrumentation", Cromewell, Wiebell, Pfeiffer

#### **References:**

1."Hand Book of Bio-Medical Instrumentation", Khandapur.McGrawHill 2."IntroductiontoBio-MedicalEquipmentTechnology",4<sup>th</sup>Edition,JosephJ.Carr,John M.Brown, Pearson Publications. **Course outcomes**

С

#### **Syllabus Details**

#### COs

- CO1 Describe the Basic Concepts of embedded systems- (K2).

- CO2 Describe the characteristics of Embedded Systems - (K2)

- CO3 Explain the Architecture and Pin Description of 8051- (K2)

- CO4 Explain various Addressing Modes and Instructions of 8051- (K2)

- CO5 Discuss the various Interrupts, Modes of Timers/Counters in 8051-(K2)

- CO6 Discuss the fundamentals of RTOS based embedded firmware design - (K2)

#### **UNIT-I - INTRODUCTION TO EMBEDDED SYSTEMS:**

Introduction to Embedded Systems, Embedded Systems vs. General Computing Systems, Classification of Embedded systems, Major application areas of embedded systems, Purpose of embedded Systems, The Typical embedded system - core of the embedded system, Difference between RISC and CISC, Types of Memories.

#### **UNIT-II - CHARACTERISTICS OF EMBEDDED SYSTEM:**

Characteristics of an embedded system, Quality attributes of embedded systems, Applicationspecific and Domain-Specific examples of an embedded system.

#### **UNIT-III-8051 Micro Controller – Architecture, Pin Description**

Introduction, 8051 Architecture, Registers in 8051, Pin Diagram - Description, Parallel I/O Ports and Memory Organization

#### **UNIT-IV - 8051 Micro Controller – Addressing Modes and Instructions:**

8051 Addressing Modes, 8051 Instruction Set, Instructions and Sample Programs, Stack Pointer

#### UNIT-V - 8051 Micro Controller - Interrupts, Timer/ Counter:

Interrupts in 8051, Timers and Counters, Timer/ Counter Modes, Serial Communication -Modes

#### UNIT-VI- REAL TIME OPERATING SYSTEM:

Operating System basics, Types of operating systems, Tasks, Process and Threads, Multiprocessing and Multitasking, Task Scheduling, Inter Task communication.

#### **Text Books:**

1. Embedded Systems-By Shibu. K.V-Tata McGraw Hill Education Private Limited, 2013.

2. Micro Controllers [Theory and Applications] – Ajay V Deshmukh – Tata McGraw-Hill Education Private Limited,2012

#### **References:**

- 1. The 8051 Micro Controller- Kenneth Ayala CENGAGE- 3rd Edition

- 2. Embedded/Real Time Systems by KVKK Prasad by Dreamtech Publication

## Course Outcomes: After Successful completion of the Course, the student will be able to:

- CO1: Analyse Image transforms for various Image processing operations(K4)

- CO2: Examine Spatial & frequency domain filtering like smoothing & sharpening Operations on Images**(K4)**

- CO3: Estimate Image degradation functions and Analyze various Image Restoration Techniques on Images**(K4)**

- CO4: Analyze various Image segmentation techniques(K4)

- CO5: Describe various Image compression techniques(K3)